基于Simulink的FPGA代码自动生成技术

课时介绍

1

课程介绍

课程主要讲解基于simulink的hdl coder模块组的使用方法,学会使用hdl coder搭建算法模型,校验模型并能自动生成可以下载到FPGA运行的Verilog或VHDL代码,学会testbench文件的自动生成和modelsim模型的验证。对于初学者,能掌握基于simulink的FPGA代码自动生成技术,会加速初学者开发复杂的FPGA算法的本领。

推荐课程

信息系统项目管理师自考笔记

李明 · 387人在学

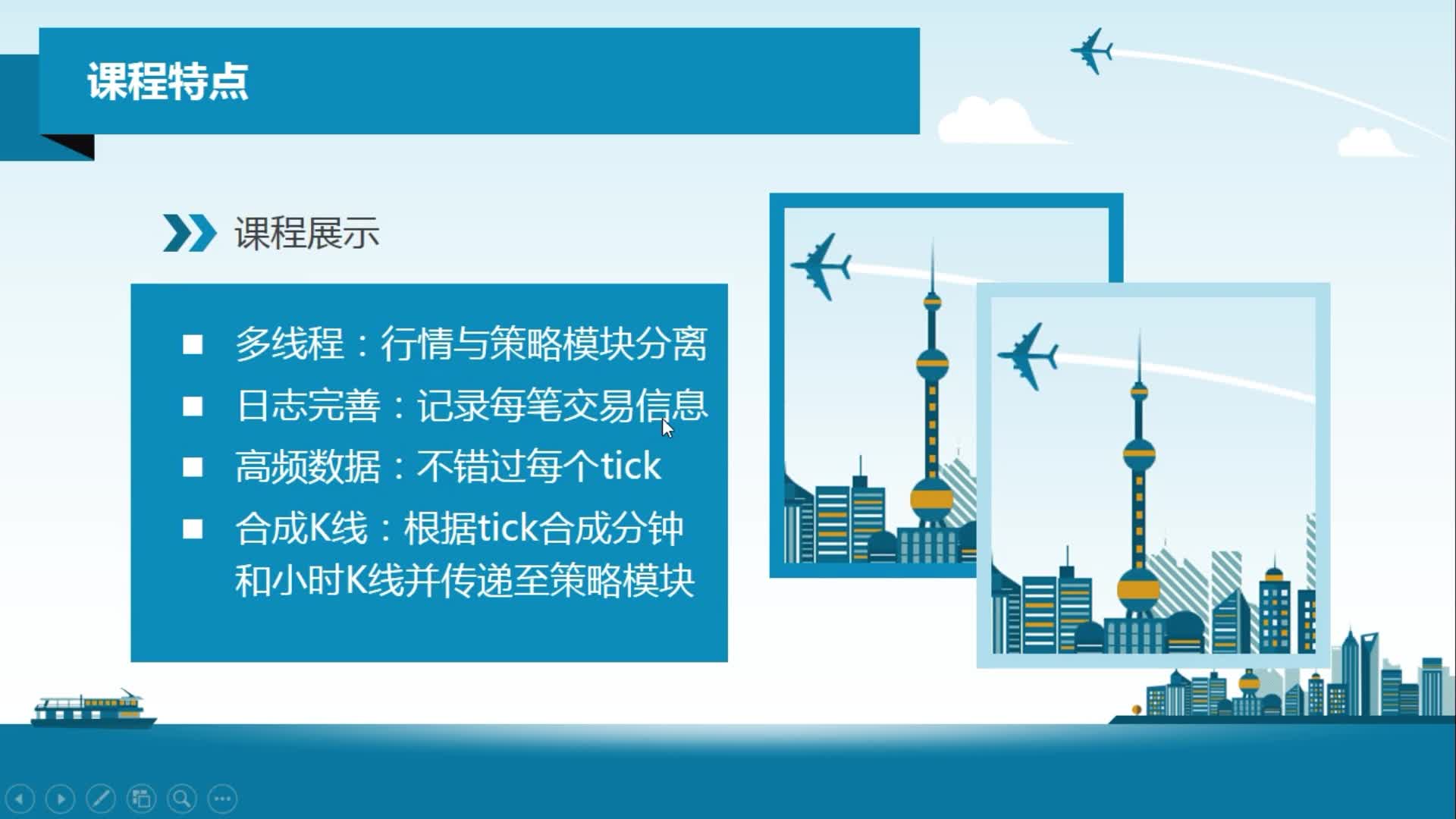

python从0到1:期货量化交易系统(CTP实战,高频及合成K线数据

王先生 · 17641人在学

手把手搭建Java超市管理系统【附源码】(毕设)

汤小洋 · 3752人在学

Java毕设springboot外卖点餐系统 毕业设计毕设源码 使用教

黄菊华 · 667人在学

基于SSM酒店管理系统(毕设)

小尼老师 · 693人在学

java项目实战之购物商城(java毕业设计)

Long · 4926人在学

手把手搭建Java求职招聘系统【附源码】(毕设)

汤小洋 · 1360人在学

Python Django 深度学习 小程序

钟翔 · 2107人在学

城管局门前三包管理系统+微信小程序(vue+springboot)

赖国荣 · 397人在学

Vue+Uni-app(uniapp)入门与实战+赠送仿美团点餐小程序

李杰 · 3534人在学